pp. 13-16

Pooja Mehra1, R. P. Gupta2, Savita Shivani1 and Naveen Hemrajani3

1 Suresh Gyan Vihar University, Jaipur

2 Manda Institute of Technology, Bikaner

3 Jaipur Engineering College & Research Centre, Jaipur

*Corresponding Author – reserachpaper26@gmail.com

ABSTRACT

This paper presents the design of programmable digital filter for transreceiver circuits. The designed filter

covers a wide range of 10 MHz – 40 MHz which covers a variety of digital wireless applications. The wide

bandwidth covers multiple wireless standards from TETRA, IS-95, GSM to TACS.

Keywords: Digital, filter, wireless

INTRODUCTION

There has been rapid growth in communication technologies in recent years. The mobile communication technology development experiences 4 stages. The first stage was from the 1920 s and 40 s where mobile communication is mainly used on ships, planes and cars, military communication system. Second stage was from the 1940 s to the 60s with the emerging of mobile phone systems. It mainly used 150 MHz VHF frequency band which further extended to 400 MHz band. The third stage was from the 1970 s to the 80s, where the concept of cellular was introduced with the use of 800 to 900 MHz band. Stage 4 extended from the 1990 s to the present day, with the introduction of digital transmission, CDMA, TDMA technology [1, 7].

The digital filters play a very important role in almost every digital transmission technology. So various researches has been done in this regard. Digital filters are an essential elements of transceivers especially with the coming in of software defined radios and cognitive radios where the digital circuitry of the radio needs to configure the filters on the fly. A digital filter system usually consists of an analog – to-digital converter to sample the input signal which is followed by a microprocessor and some peripheral components such as memory to store data and filter coefficients and finally a digital-to-analog converter completes the output stage. The microprocessor implements the digital filter by performing the necessary mathematical operations by program instructions. In some high performance applications, an FPGA or ASIC or a specialized DSP is used instead of a general purpose microprocessor with specific paralleled architecture for speeding operations such as filtering.

In comparison to analog filters, digital filters have simplified designs as they are not subject to the component non-linearities. Analog filters have imperfect electronic components having specified limit tolerances. These may also vary with temperature and drift with time. The effect of variable component errors is greatly increased with increasing order and thus component count of analog filters. Comparatively the digital filters are more stable and predictable as the coefficient values are stored in computer memory. Also the digital filters can be used to obtain more complex designs due to definite value of its coefficients. Achieving the same complex design form analog filters lead to higher engineering cost of designing. Further the coefficients of digital filters can be modified to create adaptive filters.

BACKGROUND

Wei-Kang et al have designed an optimal pulseshaping filter design for multilevel QAM/QPR digital radio systems. The design starts with the receiver filter with a magnitude optimized to a square-root. Nyquist shaping minimizes the adjacent channel interference, the AWGN channel BER. The radio test results are presented and discussed [2]. Parent et al have designed a low power and high speed 10 GHz sampling rate digital FIR filters with powers-of-two coefficients and the designed filter has applications in wireless communication in digital radio transmitter. Deep sub-micron CMOS technologies and later nanometer scale CMOS have enabled the development of highly digital radios for wireless communications. [3].Clarkson et al have worked on digital FIR filter design for spread-spectrum receivers with reduced inherent latency. The use of a programmable digital signal processor is compared to a solution which uses discrete components. Adjacent and center channel amplitudes are programmable and are programmed to change every hop period and in both amplitude and envelope [4]. Grati et al have worked on design

and hardware implementation of digital channel selection decimating filter for multistandard receiver. This paper presents a low-power design and an area-efficient FPGA implementation of designed filter. Later the design was evaluated in performance and complexity along with its support for GSM, DECT and UMTS standard [5]. Clarkson et al have reviewed digital filter design for frequency-hopping receivers. A direct-synthesis frequency synthesiser has been built which simulates the IF signal expected in the frequency-hopping radio. Even high-order filters may be designed using this technique [6].

Many techniques have been presented for the improvement of digital filter design for transceiver circuits by using various statistical and soft computing algorithms. There is a need to develop a

test bed for enabling application specific evaluation of digital filter design for software radio. Presently most of the work done has been either in the area of simulation using matlab or development of algorithms using Xilinx and other FPGA workstations. There is a need to bridge the gap between these two design methodologies

METHODOLOGY

MATLAB is used to design Digital Filters for Noise Cancellation in transceivers signal conditioning. Coding in matlab will enable VHDL interface to directly generate the vhdl code for implementation. In this paper a programmable band select filter is proposed which covers an entire range of 10Mhz-40Mhz and it can be increased beyond this range also.

RESULTS

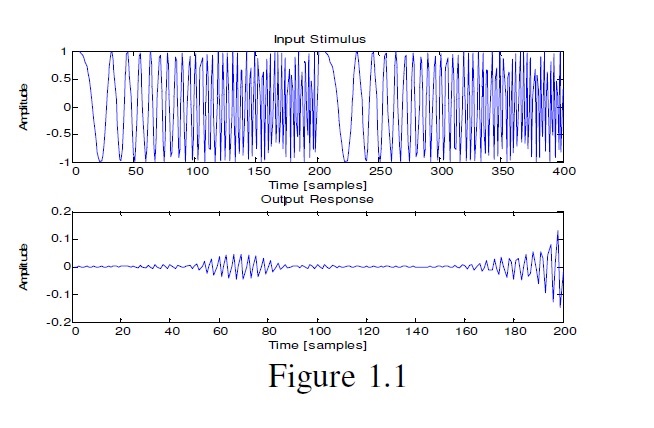

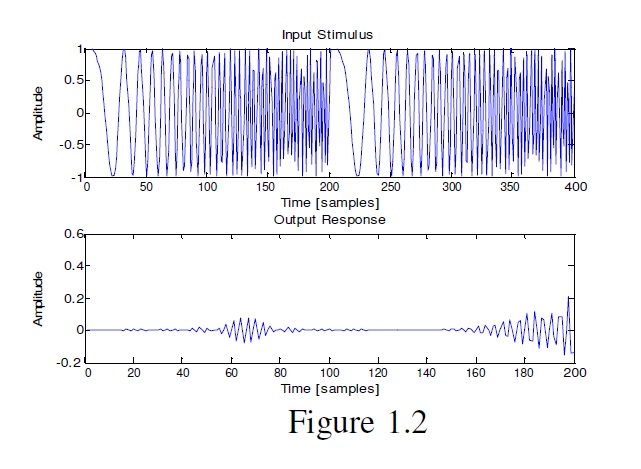

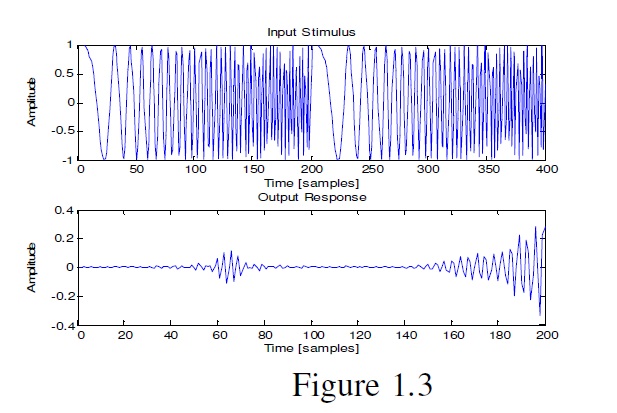

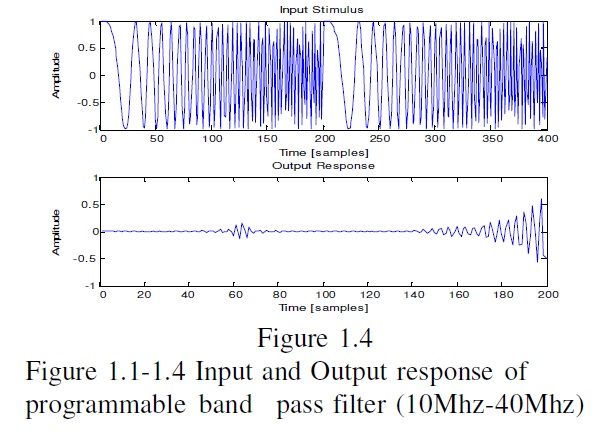

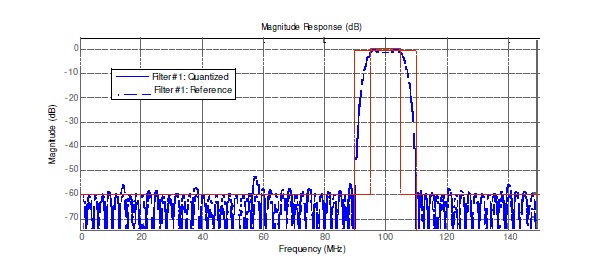

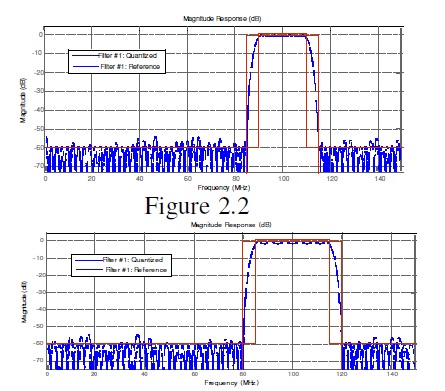

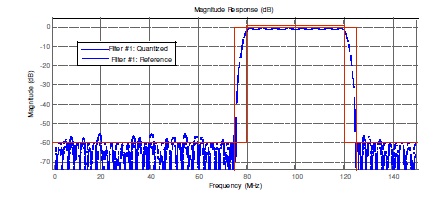

A programmable band pass filter is designed in MATLAB whose results are discussed here. The Input and filtered output for 10 MHz-40 MHz digital filter are shown in fig1.1-1.4.The magnitude responses are further shown in fig.2.1-2.4

Figure 2.1

Figure 2.3

CONCLUSION AND FUTURE SCOPE

The Filter performance is better compared to previous researches in the sense of much improved and stable response and less time consumption in its designing. The versatility of the designed filter lies in bandwidth programmability over a wide frequency domain Further the work can be extended by creating a test bed having direct interface between the matlab simulation environment and FPGA integrated development environment to design digital filters

for transceiver circuits and further analysing its performance. Xilinx IDE will be used to construct the VHDL code for Digital Filters for Noise Cancellation in Transceiver Systems.

REFERENCES:

[1] PengLin etc. The third generation mobile communication technology [M]. The first edition. Beijing: electronic industry press, 2003.8 ~ 12.

[2] Wei-Kang Cheng; Sung-Moon Yang; Jeff Jiao, “An optimal pulse-shaping filter design for multilevel QAM/QPR digital radio systems,” Communication Technology Proceedings, 1996. ICCT’96., 1996 International Conference on , vol.2, no., pp.1029,1032 vol.2, 5-7 May 1996

[3] Parent, B.; Muller, J.; Kaiser, A.; Cathelin, A., “Design of 10 GHz sampling rate digital FIR filters with powers-of-two coefficients,” Circuit Theory and Design (ECCTD), 2011 20th European Conference on , vol., no., pp.584,587, 29-31 Aug. 2011

[4] Clarkson, T.G.; Tsui, T. S D, “Digital filter design for spread-spectrum receivers,” Computer and Communication Systems, 1990. IEEE TENCON’90., 1990 IEEE Region 10 Conference on , vol., no., pp.186,189 vol.1, 24-27 Sep 1990

[5] Grati, K.; Ghazel, A.; Naviner, L., “Design and hardware implementation of digital channel selection decimating filter for multistandard receiver,” Electronics, Circuits and Systems, 2005. ICECS 2005. 12th IEEE International Conference on , vol., no., pp.1,4, 11-14 Dec. 2005

[6] Clarkson, T.G.; Tsui, T. S D, “Digital filter design for frequency-hopping receivers,”Circuits and Systems, 1990., Proceedings of the 33rd Midwest Symposium on , vol., no., pp.441,444 vol.1, 12-14 Aug 1990

[7] Zhang Ke; Zhu Qiping; Wu YunFeng, “The Design of Selecting Broad Band Signal Frequency Based on the FIR Digital Filters,” Control Engineering and Communication Technology (ICCECT), 2012 International Conference on , vol., no., pp.96,99, 7-9 Dec. 2012

[8] White, B.A.; Elmasry, M.I., “Low-power design of decimation filters for a digital IF receiver,” Very Large Scale Integration (VLSI) Systems, IEEE Transactions on , vol.8, no.3, pp.339,345, June 2000

[9] Signell, S.R.; Kouyoumdjiev, T.G.; Mossberg, K.H.; Harnefors, C.G.L., “Design and analysis of bilinear digital ladder filters,” Circuits and Systems I: Fundamental Theory and Applications, IEEE Transactions on , vol.43, no.2,

pp.69,81, Feb 1996

[10] Grati, K.; Ghazel, A.; Naviner, L., “Design and hardware implementation of digital channel selection decimating filter for multistandard receiver,” Electronics, Circuits and Systems, 2005. ICECS 2005. 12th IEEE International Conference on , vol., no., pp.1,4, 11-14 Dec. 2005

[11] D”Andrea, A.N.; Guglielmi, F.; Mengali, U.; Spalvieri, A., “Design of transmit and receive digital filters for data communications,” Communications, IEEE Transactions on , vol.42, no.234, pp.357,359, Feb/Mar/Apr 1994.